# Nano Field Effect Transistors as basic building blocks for sensing

### Inauguraldissertation

zur

Erlangung der Würde eines Doktors der Philosophie

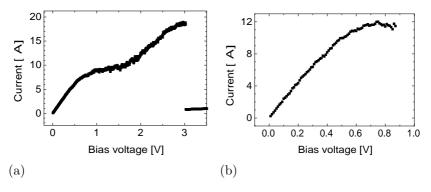

vorgelegt der

Philosophisch-Naturwissenschaftlichen Fakultät

der Universität Basel

von

Dino Keller aus Bischofszell, TG

Basel, 2008

Genehmigt von der Philosophisch-Naturwissenschaftlichen Fakultät auf Antrag von

Prof. Dr. C. Schönenberger

Prof. Dr. A. Ionescu

Prof. Dr. A. Engel

Dr. M. Calame

Basel, den 11. Dezember 2007

Prof. Dr. Hans-Peter Hauri Dekan

It is the glory of God to conceal a thing: but the honour of kings is to search out a matter.

King Solomon, Proverbs 25: 2

# Contents

| 1 | Intr | ntroduction |                           |    |

|---|------|-------------|---------------------------|----|

|   | 1.1  | Motiva      | ation                     | 1  |

|   | 1.2  | About       | this work                 | 2  |

| 2 | The  | eoretic     | al background             | 5  |

|   | 2.1  | Standa      | ard FET theory            | 5  |

|   |      | 2.1.1       | MOS capacitor terminology | 7  |

|   |      | 2.1.2       | Surface depletion         | ç  |

|   |      | 2.1.3       | MOS capacity              | 11 |

|   |      | 2.1.4       | Subthreshold regime       | 12 |

|   | 2.2  | Nanov       | vire FETs                 | 13 |

ii Contents

|   | 2.3 | Carbo   | n Nanotube FETs                              | 14 |

|---|-----|---------|----------------------------------------------|----|

|   |     | 2.3.1   | Introduction to Carbon Nanotubes             | 14 |

|   |     | 2.3.2   | Carbon Nanotube MOSFET model                 | 17 |

|   |     | 2.3.3   | CNT Schottky Barrier Transistor model        | 23 |

|   |     | 2.3.4   | Experimental observations: Literature review | 25 |

| 3 | Sen | sor fal | orication techniques                         | 27 |

|   | 3.1 | Silicon | NW FET                                       | 28 |

|   |     | 3.1.1   | Top oxide                                    | 30 |

|   |     | 3.1.2   | Etching mask                                 | 30 |

|   |     | 3.1.3   | Etching of the device structure              | 32 |

|   |     | 3.1.4   | Contacts                                     | 36 |

|   |     | 3.1.5   | Summary SiNW FET devices                     | 36 |

|   | 3.2 | Carbo   | n Nanotube FET                               | 38 |

|   |     | 3.2.1   | General device fabrication issues            | 39 |

|   |     | 3.2.2   | Chemical Vapor Deposition                    | 41 |

|   |     | 3.2.3   | Selection and location                       | 43 |

|   |     | 3.2.4   | Contacting CNTs                              | 45 |

|   |     | 3.2.5   | Summary CNT FET fabrication                  | 46 |

|   | 3.3 | Packag  | ging                                         | 48 |

| 4 | Cha | aracter | ization of SiNW and CNT FETs                 | 49 |

|   | 4.1 | Silicon | Nanowire FET characterization                | 49 |

|   |     | 4.1.1   | Accumulation regime                          | 50 |

|   |     | 4.1.2   | Depletion regime                             | 53 |

Contents

|   |     | 4.1.3  | Weak inversion regime                                 | 55  |

|---|-----|--------|-------------------------------------------------------|-----|

|   |     | 4.1.4  | Strong inversion regime                               | 57  |

|   |     | 4.1.5  | Capacitance of gate coupling                          | 58  |

|   |     | 4.1.6  | Geometrical consideration                             | 62  |

|   |     | 4.1.7  | Hysteresis                                            | 66  |

|   |     | 4.1.8  | Summary SiNW FETs                                     | 68  |

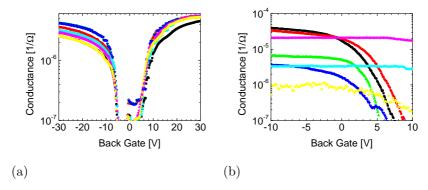

|   | 4.2 | Carbo  | on Nanotube FET characterization                      | 68  |

|   |     | 4.2.1  | Threshold voltage                                     | 70  |

|   |     | 4.2.2  | On-conductance                                        | 70  |

|   |     | 4.2.3  | Slope in transfer characteristic                      | 72  |

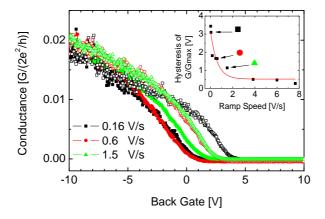

|   |     | 4.2.4  | Hysteresis                                            | 73  |

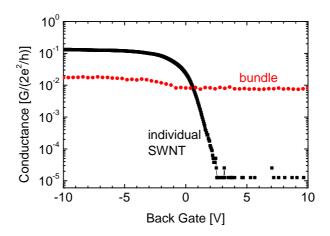

|   |     | 4.2.5  | Bundles versus individual nanotubes                   | 75  |

|   |     | 4.2.6  | Summary CNT FETs                                      | 78  |

| 5 | Env | ironm  | ental Effects on Nano FETs                            | 79  |

|   | 5.1 | Introd | luction                                               | 79  |

|   |     | 5.1.1  | Chemical sensors on basis of MOSFETs                  | 79  |

|   |     | 5.1.2  | Going for nano                                        | 82  |

|   | 5.2 | Setup  | for test in liquid                                    | 85  |

|   | 5.3 | SiNW   | FETs in liquid                                        | 87  |

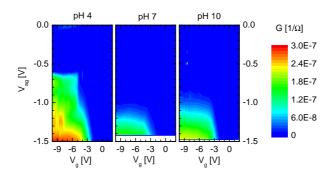

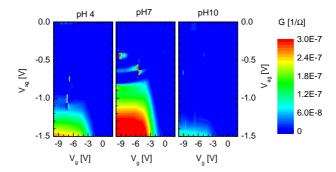

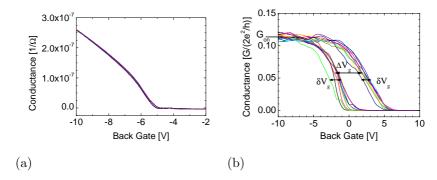

|   |     | 5.3.1  | Transfer characteristic in liquid environment $\dots$ | 88  |

|   |     | 5.3.2  | Electrolyte gating                                    | 88  |

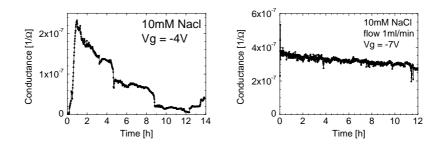

|   |     | 5.3.3  | Stability of SiNW FETs liquid setup                   | 98  |

|   |     | 5.3.4  | Summary                                               | 101 |

iv Contents

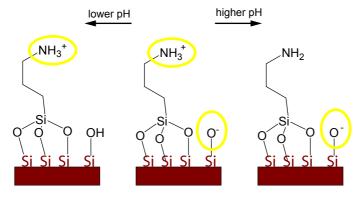

|              | 5.4  | pH ser  | nsitivity of SiNW FETs                | 101 |

|--------------|------|---------|---------------------------------------|-----|

|              | 5.5  | Sensiti | ivity of CNT FETs                     | 105 |

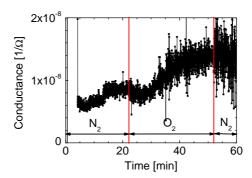

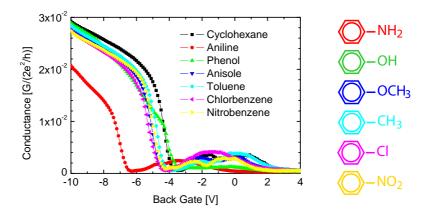

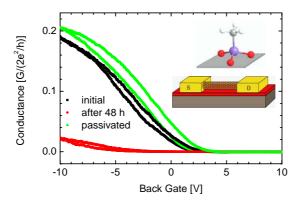

|              |      | 5.5.1   | Sensitivity of CNT FETs to adsorbates | 105 |

|              |      | 5.5.2   | Electrolyte gating                    | 108 |

|              |      | 5.5.3   | Gating by dipole orientation          | 111 |

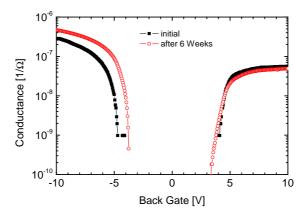

|              | 5.6  | Stabili | ty of CNT FETs                        | 112 |

|              |      | 5.6.1   | Carbon Nanotube - Metal contacts      | 113 |

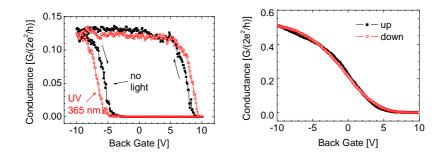

|              |      | 5.6.2   | Surface charges on the substrate      | 120 |

|              |      | 5.6.3   | Degradation of CNT FETs               | 121 |

| 6            | Fina | al com  | parison and outlook                   | 125 |

|              | 6.1  | Fabric  | ation Issues                          | 125 |

|              | 6.2  | Transi  | stor behavior                         | 127 |

|              | 6.3  | Sensin  | g with Nano FETs                      | 129 |

|              | 6.4  | Summ    | ary and Outlook                       | 131 |

| $\mathbf{A}$ | Elec | ctronic | properties of CNTs                    | 135 |

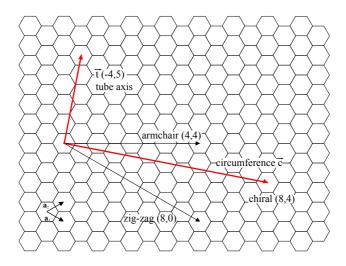

|              | A.1  | Struct  | ural properties of CNTs               | 135 |

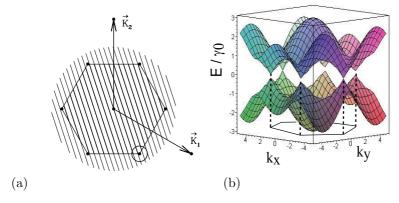

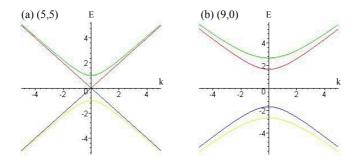

|              | A.2  | Electro | onic properties of Carbon Nanotubes   | 138 |

|              |      | A.2.1   | Overview                              | 138 |

|              |      | A.2.2   | Graphene                              | 139 |

|              |      | A.2.3   | Band structure of Carbon Nanotubes    | 139 |

|              |      | A.2.4   | Band structure near the Fermi points  | 141 |

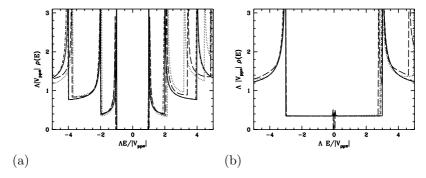

|              |      | A.2.5   | Density of States in Carbon Nanotubes | 143 |

Contents

| В            | Supporting measurements |                                               |     |  |  |

|--------------|-------------------------|-----------------------------------------------|-----|--|--|

| $\mathbf{C}$ | Methods                 |                                               |     |  |  |

|              | C.1                     | TMAH etching                                  | 151 |  |  |

|              | C.2                     | Chemical Vapor Deposition of Carbon Nanotubes | 154 |  |  |

|              | C.3                     | Alternative fabrication approaches            | 158 |  |  |

|              | C.4                     | E-beam lithography                            | 161 |  |  |

|              | C.5                     | Metal deposition                              | 161 |  |  |

|              | C.6                     | Surface manipulation                          | 162 |  |  |

| D            | List                    | of Symbols                                    | 163 |  |  |

vi Contents

# CHAPTER 1

Introduction

#### 1.1 Motivation

Chemical and biological sensing are old fields but of increasing interest. The goal of any chemical or biological sensing scheme is to detect a particular molecule. This is done by monitoring a specific binding or reaction between the molecules of interest — the so called analyte — and a well known recognizing molecule. In nondestructive analysis methods this is done by making use of physical properties of this bound pair or new product. Examples of such techniques are optical spectroscopy, chromatography, mass spectroscopy or precipitation. Today's demand is not only for detecting one specific analyte, but more and more for systematic analysis. Therefore the integration of a huge amount of analysis tools into an automatized process is required. Industry and basic science could both

2 Introduction

profit from such systems. Ideas range from automatized health monitoring in medicine to most detailed analysis of complex biological systems in systems-biology. Traditional analysis techniques hardly can meet the requirements of such an integration. Simple interfaces to computerized aquisition and controlling systems and minituarization are key factors. In computer industry a breakthrough was the step from fabricating and combining individual transistors to integrated chips where a complete system is fabricated at once. In analogy to this one would like to fabricate a complete bio-chemical lab integrated in combination with microfluidics onto a single chip. Such a device is simply called Lab-On-Chip.

To implement sensors in such a Lab-On-Chip an interface is needed to transduce a chemical binding event into an electronic signal. In this context it is naturally to study the response of semiconductors to their chemical environment. At the surface of a semiconductor, charges can be induced by the local electrical potential of nearby molecules. Such charges influence the conductance of the semiconductor. Changes in its conductance can easily be measured by contacting the semiconductor to an electronic setup. By a third electrode — the gate electrode — an electric field can be applied to induce extra charges. This way we have a Field Effect Transistor (FET) where the current for fixed bias voltage can be controlled by a gate electrode on one hand and on the other hand by charges of chemical species at the semiconductor surface.

Requirements for FETs are different in this context than in the context of computing by logic switching. The semiconductor as sensitive part has to be exposed to the media of interest. It has to be small but with high surface area as sensing is a surface effect. To be more precise the ratio between surface charges and the total number of current carrying charges has to be high. For many Lab-On-Chip applications sensitivity to a small amount of analyte molecules is desired.

#### 1.2 About this work

Ideal candidates for such FETs are Silicon Nanowire FETs and Carbon Nanotube FETs. The two are investigated experimentally in this work.

1.2. About this work

For both types of devices, pioneering sensing assays have been reported (see Section 5.1.2 for a small literature review). Here we focus on an improved control over device fabrication and performance.

In Chapter 2 the working principle of conventional MOSFETs is introduced and silicon nanowire FETs are described as a special case of MOSFETs. To describe carbon nanotube FETs a small model is presented based on the MOSFET theory.

The design and fabrication of the two types of nano FETs is described in Chapter 3. General design and process considerations are discussed as well as fabrication details.

Chapter 4 elaborates the FET behavior of the silicon nanowire and carbon nanotube FETs.

The potential for sensing application of silicon nanowire and carbon nanotube FETs is discussed in Chapter 5. It begins with an introduction in MOSFET based chemical and biological sensing. The study of silicon nanowire FETs in liquid environment shows pH sensitivity and that good control of the hole system is mandatory. For carbon nanotube FETs the extremely high sensitivity is shown as well as challenges in reliability.

A comparison of the two systems in Chapter 6 summarizes and concludes this work.

4 Introduction

# CHAPTER 2

Theoretical background

### 2.1 Standard FET theory

This Section gives a short introduction to standard Field effect Transistor theory. It is intended for readers that are not familiar with the terminology and working principle of FET devices. Readers who are interested in more details should consult a standard textbook on semiconductor devices as the well known book from Sze [1] or the online book from Van Zeghbroeck [2].

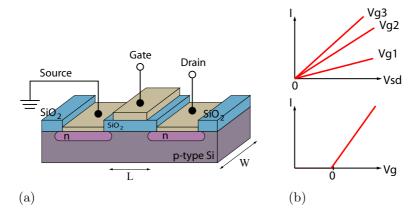

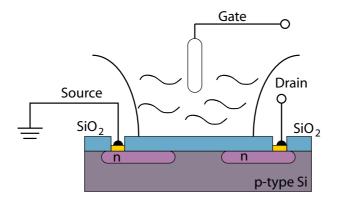

The geometry of a standard Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is shown in Figure 2.1 (a). Two highly n-doped contact regions are separated by the low p-doped substrate. Because of the two p-n junctions no current can flow, even if a bias is applied between source and drain contacts. At the surface of the semiconductor, between the

Figure 2.1: (a) Schematics of a MOSFET. (b) Simplified current vs. bias (top) and gate voltage (bottom) characteristics.

contact regions, there is a metal gate electrode separated by an insulating oxide layer. Electrons can be induced at the semiconductor—oxide interface when a positive voltage is applied to the gate. In this case a current flows. In a linear model it is proportional to the amount of induced electrons. In Figure 2.1(b) the current is sketched as function of a voltage applied between source and drain  $V_{sd}$  and a voltage applied to the metal gate  $V_g$ . As long as the bias applied between source and drain is not too high, the current density can be described by Ohms law

$$\vec{j} = \sigma \vec{E}, \qquad j = \sigma \frac{V_{sd}}{L}$$

where  $|\vec{E}| = V_{sd}/L$  is the applied electric field with the source - drain bias  $V_{sd}$  and L the length of the separation between the contact regions. The conductivity  $\sigma$  is given by the Drude model as  $\sigma = en\mu$  with the carrier mobility  $\mu$  and the carrier concentration n [3].

To deduce the carrier concentration n we look at the capacitor made up of the metal gate, oxide insulator and the semiconductor. In a first step, we

assume it to behave as a perfect plate capacitor not depending on applied voltages. The induced charge is given by the product  $Q = C_g \cdot V_g$  of the capacitance  $C_g$  and the applied gate voltage  $V_g$ . The charge density follows as  $en = C_g'V_g/h_s$  with the height of the charge carrier sheet  $h_s$  and the capacitance per unit area  $C' = C/(W \cdot L)$ . Assuming that the mobility and the gate capacitance  $C_g$  are independent of the applied voltages and assuming no intrinsic charges, the current is given by

$$I = Wh_s j = Wh_s e \mu n \frac{V_{sd}}{L} = \frac{W}{L} \mu C_g' V_g V_{sd}. \tag{2.1}$$

This is the most basic transistor relation. The way it has to be modified when the above assumptions are generalized depends on the specific system. We have to treat MOSFETs, nanowire FETs and carbon nanotube FETs separately. The case of MOSFETs is briefly discussed first. In Section 2.2 modifications for the case of nanowire FETs are explained. Nanotube FETs are discussed in Section 2.3 following the same line as the discussion below.

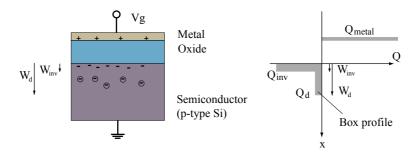

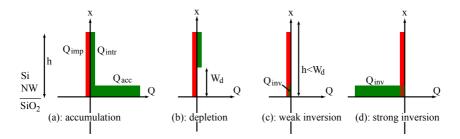

#### 2.1.1 MOS capacitor terminology

First we discuss the metal oxide semiconductor (MOS) capacitor shown in Figure 2.2. We discuss the situation of a p-type semiconductor. When applying a negative voltage on the gate electrode, holes are accumulated in the semiconductor. These holes are at the interface to the oxide within a thin layer, the so-called accumulation layer. When a positive voltage is applied, the intrinsic holes have to be depleted. In the depletion region, there are no mobile charges, but only the immobile acceptor ions. To simplify, the depletion approximation is used which assumes that the depleted charge  $Q_d$  has a box profile of width  $W_d$  as sketched in Figure 2.2. Thus  $Q_d = -eN_aW_d$  with the acceptor dopant density  $N_a$  and the elementary charge e. When the gate voltage is driven further, electrons are induced at the interface. They build up the inversion charge  $Q_{inv}$  in the thin inversion layer of width  $W_{inv}$ .

The transfer from accumulation to depletion region occurs at finite voltage  $V_{fb}$  called flat band voltage. It is the voltage at which the bands in the

Figure 2.2: Metal Oxide Semiconductor (MOS) structure in inversion regime.

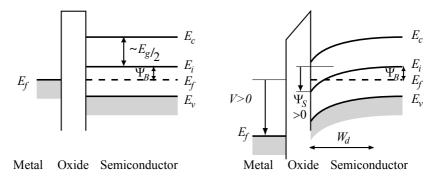

semiconductor are flat all the way from the bulk to the oxide interface as shown on the left side of Figure 2.3. In the ideal case the flat band voltage is given by difference in work function of the metal  $\phi_m$  and the silicon  $\phi_s$ :  $V_{fb} = \phi_m - \phi_s$ . In real devices one has to consider charges within the oxide  $Q_{ox}$ . They contribute via the gate capacitance  $C_g$  so that the total flat band voltage is given by

$$V_{fb} = \phi_m - \phi_s - \frac{Q_{ox}}{C_q}. (2.2)$$

The potential difference between the Fermi energy and the middle of the band gap is given by  $\Psi_B$  as sketched in Figure 2.3. If a voltage different than the flat band voltage is applied on the gate, the bands are bent towards the interface. The potential at the interface with respect to the intrinsic energy level  $E_i$  is called  $\Psi_s$  (Figure 2.3 right). It is defined to be positive when the bands bend downwards. In the bulk of the semiconductor the bands are not affected. There the potential  $\Psi_B$  remains, and therefore it is called "bulk potential". With these definitions we have a measure for the different regimes mentioned in the previous paragraph. We have:

Figure 2.3: Band bending in MOS structure for p-type semiconductor in flat band condition (left) and in weak inversion (right). Energies are indicated for conduction band  $E_c$ , valence band  $E_v$ , band gap  $E_g$ , intrinsic energy (mid-band)  $E_i$  and Fermi energy  $E_f$ .

| $\Psi_s < 0$                | Accumulation of holes                       |

|-----------------------------|---------------------------------------------|

| $\Psi_s = 0$                | Flat band condition                         |

| $0 < \Psi_s < \Psi_B$       | Depletion of holes                          |

| $\Psi_s = \Psi_B$           | Fermi level at midgap, at interface $n = p$ |

| $\Psi_B < \Psi_s < 2\Psi_B$ | Weak inversion, at interface $n > p$        |

| $2\Psi_B < \Psi_s$          | Strong inversion, at interface $n > N_a$    |

#### 2.1.2 Surface depletion

Depletion at the semiconductor surface occurs whenever the surface potential  $\Psi_s > 0$ . In a MOS structure this might be caused by a gate voltage. In general, at any semiconductor surface, the potential can be shifted by surface charges or surface states. Such surface states can come from perturbation of the bulk band structure at the interface [4, 5].

In a doped semiconductor free carriers can fill these surface states which leads to a surface charge  $n_s$  and an oppositely charged depletion region below the surface that can be more extended. We look at the case of

p-type semiconductor with acceptor concentration  $N_a$ . In the depletion region all acceptors are ionized giving a space charge density of  $-eN_a$  and a total depletion region charge of  $-eN_aW_d$ . The potential is described by the Poisson equation

$$\frac{d^2\Psi}{dx^2} = \frac{eN_a}{\varepsilon_r \varepsilon_0} \Rightarrow \Psi = \frac{eN_a}{2\varepsilon_r \varepsilon_0} (x - W_d)^2.$$

(2.3)

The potential at the interface is given by the surface potential  $\Psi(0) = \Psi_s$ . With this we can get the depletion width:

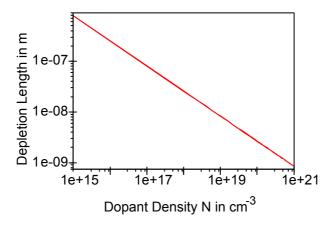

$$W_d = \sqrt{\frac{2\varepsilon_r \varepsilon_0 \Psi_s}{eN_a}}. (2.4)$$

Figure 2.4: Depletion width as function of dopant density for silicon for surface potential  $\Psi_s = E_g/2$ .

In Figure 2.4 the depletion width is plotted as function of the dopant density of silicon. The surface potential is assumed to have the size of half the band gap  $\Psi_s = E_g/2$ .

#### 2.1.3 MOS capacity

In a MOS capacitor the voltage applied on the gate partially drops across the insulator and partly within the semiconductor

$$V_q = V_i + V_s$$

.

The voltage drop within the semiconductor corresponds to the surface potential  $\Psi_s$  and the voltage drop across the insulator is given by the charge  $Q_s$  on the semiconductor

$$V_i = |\vec{E}|d = \frac{Q_s/Ad}{\varepsilon_{SiO_2}\varepsilon_0} = \frac{Q_s}{C_{ox}}.$$

with the oxide capacitance  $C_{ox} = A\varepsilon_{SiO_2}\varepsilon_0/d$  where d is the thickness of the oxide and A the area of the interface. With this the relation between the applied gate voltage and the surface potential is

$$V_g = \Psi_s + \frac{Q_s}{C_{ox}} \tag{2.5}$$

In MOSFETs the gate voltage that has to be applied to reach the onset of strong inversion is called threshold voltage

$$V_{th} = V_{fb} + 2\Psi_B + \frac{Q_s}{C_{ox}}. (2.6)$$

The relation between the surface potential and the induced charge can be described by the semiconductor capacitance  $C_s = dQ_s/d\Psi_s$ . This capacitance depends very much on type of system we are looking at (more details in Section 2.2). In case of a standard MOS capacitor, we can think of a depletion layer capacitance  $C_d = dQ_s/d\Psi_s$ . This capacitance depends on the applied voltage and on the frequency of charging. In depletion regime one can think of it as a plate capacitor with plates separated by the depletion width  $C_d = A\varepsilon_{Si}\varepsilon_0/W_d$ .

The total gate capacitance is the series capacitance of the oxide capacitance and the depletion capacitance

$$C_g^{-1} = C_{ox}^{-1} + C_d^{-1}.$$

In accumulation and strong inversion the depletion width goes to zero and the total gate capacitance  $C_q$  is dominated by  $C_{ox}$ .

#### 2.1.4 Subthreshold regime

In depletion or weak inversion the electrostatics in the semiconductor is dominated by the charge of the immobile ions in the depletion region  $-eN_aW_d$  as described in Section 2.1.1. But now we are interested in the small mobile charge that can be thermally excited in the depletion zone because this gives rise to a small subthreshold current. The carrier concentration far away from the Fermi energy is given by the Boltzmann distribution  $n = n_i \exp(-e\Psi/kT)$  and so

$$Q=e\int_0^{W_d}n(x)dx=e\int_{\Psi_s}^0\frac{n(\Psi)}{d\Psi/dx}d\Psi=en_i\int_{\Psi_s}^0\frac{1}{d\Psi/dx}e^{-\frac{e\Psi}{kT}}d\Psi.$$

With  $d\Psi/dx$  from Equation 2.3 the integral approximatively [6] gives

$$Q = kT \sqrt{\frac{\varepsilon_0 \varepsilon_{Si}}{2e\Psi_s N_a}} \left(\frac{n_i}{N_a}\right)^2 e^{-e\Psi_s/kT}.$$

The square-root term is a much weaker function of  $\Psi_s$  compared to the exponential term and can be treated as constant [1]. Thus the mobile charge in the depletion region and with it the current in the subthreshold regime depend exponentially on the surface potential  $\Psi_s$ :  $I \propto \exp(-e\Psi_s/kT)$ . To relate this to the applied gate voltage we calculate  $dV_g/d\Psi_s$  from Equation 2.5 including  $C_d = dQ_s/d\Psi_s$ :

$$\frac{dV_g}{d\Psi_s} = 1 + \frac{C_d}{C_{ox}}.$$

The subthreshold swing S is defined as the gate voltage change needed to suppress the subthreshold current by one order of magnitude:

$$S = \left| \frac{dV_g}{d(\log(I))} \right| = \left| \ln(10) \frac{dV_g}{d(\ln(I))} \right| = \ln(10) \frac{dV_g}{e/kT d\Psi_s}$$

$$= 59.6 \,\text{mV} \frac{kT}{e} \left( 1 + \frac{C_d}{C_{ox}} \right). \tag{2.7}$$

Interface trap states at the semiconductor – oxide interface lead to an extra capacitance per area  $C'_{it} = e^2 D_{it}$  in parallel with the depletion layer capacitance per area  $C'_{d} = C_{d}/A$  and  $C'_{ox} = C_{ox}/A$ .  $D_{it}$  is the density of interface traps per energy and area. The modified subthreshold swing is

$$S = \ln(10)\frac{kT}{e} \left( 1 + \frac{C'_d + e^2 D_{it}}{C'_{or}} \right).$$

(2.8)

With higher trap state density  $D_{it}$  the subthreshold slope is less sharp.

#### 2.2 Nanowire FETs

In CMOS technology down-scaling is driven by the need of ever higher integration. The channel length L is pushed down further and further and with it the gate oxide thickness, applied voltages and device resistance. In contrast to this the channel length L of nanowire FETs and nanowire like structures is much larger than the channel width W. Short channel effects don't come into play as the gate insulator thickness d is smaller than the channel length L. But the diameter of the nanowire semiconductor body is now much smaller than the depletion width (see Figure 2.4). Therefore we have to reconsider the semiconductor capacitance. From equation 2.5 we get for the MOS structure  $V_g = \Psi_s + |Q_s|/C_{ox}$ . As the semiconductor body is too thin, the last term cannot be related to the depletion capacitance as we used to do for the standard MOS structure. We use a more general expression for the relation between the semiconductor charge and the surface potential  $dQ_s/d\Psi_s = Aedn/d\Psi_s = C_s$  leading to the general semiconductor capacitance  $C_s$ . With this we get the relation

$$\frac{dV_g}{d\Psi_s} = 1 + \frac{C_s(\Psi_s)}{C_{or}}. (2.9)$$

Let's consider two special cases. If the gate oxide layer is much thicker than the charge layer in the semiconductor, we are in the regime of  $C_{ox} \ll C_s$ . In this case gate variations lead to

$$dV_g \approx d\Psi_s C_s / C_{ox} = e dn / C_{ox}.$$

The gate voltage directly controls the charge in the semiconductor as described in the standard MOSFET theory (Equation 2.1). In a standard MOSFET the oxide thickness d is much larger than the inversion layer width  $W_{inv}$ . In the case of  $C_{ox} \gg C_s$  Equation 2.9 simplifies to  $V_g = \Psi_s + \text{const.}$  The gate voltage directly controls the surface potential  $\Psi_s$  of the semiconductor [7]. The ratio of these two capacitances has to be studied when scaling the oxide or the bulk silicon down.

In a semiconductor any local charge is screened within the so-called Debye screening length  $L_D = \sqrt{kT\varepsilon_0\varepsilon_{Si}/ne^2}$  which is in the range of  $L_D = 40\,\mathrm{nm}$  for  $n = 10^{16}\,\mathrm{cm}^{-3}$  [1]. If the wire is smaller than the Debye screening length  $L_D$ , surface charges cannot be screened. For thin wires the carrier density n gets more and more uniform within the wire cross-section. The same holds for the Fermi energy within the wire which is now equal to the surface potential  $E_f = e\Psi_s$ . In this case the carrier density in the semiconductor is described by the density of states (DOS). The semiconductor capacitance in this special case is called quantum capacitance  $C_q$  and  $C_q' = C_q/A$  is

$$C_q' = e \frac{dn}{d\Psi_s} = e \frac{dn}{dE_f/e} = e^2 \cdot DOS(E = E_f). \tag{2.10}$$

In the subthreshold regime the Fermi energy is in the band gap and therefore the DOS is zero. The subthreshold swing S given in Equation 2.7 is reduced and ideally reaches its limit [8, 9, 10]

$$S = \ln(10) \frac{kT}{e} \left( 1 + \frac{C'_q}{C'_{ox}} \right) \approx \ln(10) \frac{kT}{e} = 60 \,\text{mV/dec}, \quad T = 300 \,\text{K}.$$

(2.11)

#### 2.3 Carbon Nanotube FETs

#### 2.3.1 Introduction to Carbon Nanotubes

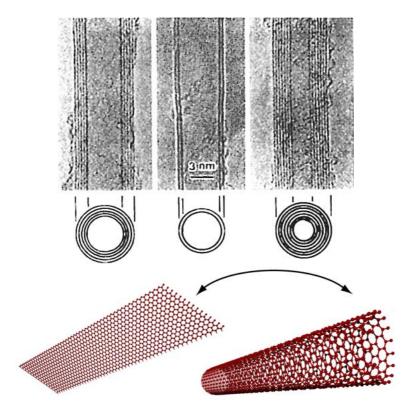

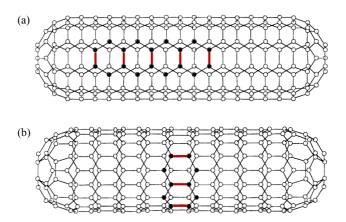

Since carbon nanotubes (CNTs) were discovered by Iijima in 1991 [11] they made their way in many different fields of research and applica-

tions. The reason is their various fascinating properties. With a typical diameter of 1-20 nm they can reach a length of millimeters [12]. Being all of carbon they are chemically inert and they are very strong. Their Young's modulus is estimated to be around 1 TPa [13], which is the highest ever reported. They can be metallic or semiconducting, depending on their atomic arrangement (see Appendix A). One can think of carbon nanotubes as a sheet of graphene rolled up (see Figure 2.5). There can be multiple shells cylindrically within each other as shown in the TEM image of Figure 2.5. Such nanotubes are called multi-walled carbon nanotubes (MWNTs). In the following context we are interested in single-walled carbon nanotubes (SWNTs) unless specifically mentioned. A more detailed introduction into carbon nanotubes and their electronic properties can be found in the Appendix A.

The fact that there are semiconducting carbon nanotubes brought quickly the idea of building field-effect transistors. This was realized by Tans et al. [14] in 1998. In the last few years much effort was put into understanding and improving such carbon nanotube field effect transistors (CNT FETs). Even logic circuits consisting of several CNT FETs have been realized [15, 16].

There are two different approaches that are often used to model CNT FETs: the model of MOSFET-like structures and the model of Schottky barrier transistors (SBFETs).

- 1. In a traditional Si MOSFET (see Section 2.1) source and drain regions are highly doped, whereas the channel is undoped or oppositely doped (see Figure 2.1). An insulating oxide layer separates the metal gate from the channel. By applying a gate potential, an inversion layer is formed. A bias between source and drain leads to a current flow. The resistance of the transistor is tuned by varying the number of induced carriers via the gate.

- 2. In Schottky barrier transistors the semiconducting channel is contacted by metal electrodes. At the contacts, Schottky barriers are present. The transistor operates by modulating the width of the tunnel barrier and, therefore, the current that flows from the contact.

Figure 2.5: Top: TEM image of multi–walled carbon nanotubes, adopted from [11]. Bottom: Schematics of a sheet of graphene and a single walled carbon nanotube.

The first CNT FETs were described by charge modulation [14] in a MOS-FET approach. The Schottky barrier model [17] was introduced explaining ambipolar behavior. The two models will be introduced next and compared in Section 2.3.4.

#### 2.3.2 Carbon Nanotube MOSFET model

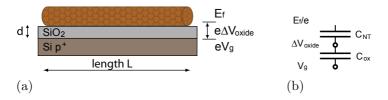

An applied gate voltage  $V_g$  will induce charge carriers in the nanotube that can contribute to a current passing the NT. Section 2.10 shows in general that depending on the semiconductor capacitance, the induced charge density might not linearly depend on the gate voltage. But the surface potential — which corresponds to the Fermi energy in case of nanotubes — can be related to the applied voltage. For this reason we are going to estimate the Fermi energy within the CNT when a gate voltage  $V_g$  is applied, then we will calculate the number of induced carriers from the Fermi energy and finally estimate the conductance G as function of the back—gate voltage  $V_g$ .

In analogy to the MOSFET theory where the MOS capacitance is studied, we first look at the silicon-oxide-CNT structure here (Figure 2.6 (a)). The capacitance C = dQ/dV of this structure is best described by the model of a thin metallic wire at distance d from an infinitely large metallic plate [18]. If the radius of the wire r is much smaller than the distance to the metal plate  $r \ll d$  a simple solution can be given for the capacitance per unit length  $C_{ox}^* = C_{ox}/L$ :

$$C_{ox}^{\star} = \frac{2\pi\varepsilon_0\varepsilon_r}{\ln\left(\frac{2d}{r} + 2\right)} \sim 20 \,\mathrm{pF/m}.$$

(2.12)

The nanotube is not surrounded by one single gate dielectric. Between the gate and the nanotube there is  $\mathrm{SiO}_2$  with  $\varepsilon_{SiO_2} \approx 3.9$ , whereas above is air with  $\varepsilon_{air} \approx 1$ . This has to be taken into account by an effective dielectric constant  $\varepsilon_r^{eff} \sim \varepsilon_{SiO_2}/2 \sim 2$  as shown in [18] and [19]. With an oxide spacing of  $d=400\,\mathrm{nm}$  and a tube radius of  $r=2\,\mathrm{nm}$  this leads to  $C_{ox}^{\star} \sim 20\,\mathrm{pF/m}$ .

Figure 2.6: Silicon-oxide-CNT structure (a) with analogous circuit (b) consisting of oxide capacitance  $C_{ox}$  and quantum capacitance  $C_{NT}$ .

The CNT in a silicon-oxide-CNT structure cannot completely screen the electric field of the applied gate voltage as a metallic capacitor plate could. The potential within the CNT in not zero, but corresponds to the local Fermi energy  $E_f$ . The potential drop in the oxide is the difference between the applied voltage and the potential of the Fermi Energy within the CNT

$$V_g - \frac{E_f}{e} = \Delta V_{ox} = \frac{Q_{ind}}{C_{ox}}$$

where  $Q_{ind}$  is the total induced charge and  $C_{ox} = C_{ox}^{\star} \cdot L$  is the oxide capacitance (Equation 2.12).

How does the Fermi Energy depend on the applied gate voltage? We take the derivative

$$\frac{dV_g}{dE_f} = \frac{1}{e} + \frac{1}{C_{ox}} \frac{dQ_{ind}}{dE_f} = \frac{1}{e} \left( 1 + \frac{C_{NT}}{C_{ox}} \right)$$

(2.13)

with the quantum capacitance  $C_{NT} = e \cdot dQ_{ind}/dE_f$ . The quantum capacitance is given by the density of states (Equation 2.10) because with the one dimensional carrier density n, the total induced charge per unit energy is  $dQ_{ind}/dE_f = eL \cdot dn/dE_f = eL \cdot \text{DOS}$ . With this, we can give an approximation for the quantum capacitance for energies well above the band edge. There the density of states is  $\text{DOS} = 8/(3\pi a_{CC}\gamma) = 2.0 \cdot 10^9 \, (\text{m} \cdot \text{eV})^{-1}$  (see Appendix Equation A.15 for derivation) and the quantum capacitance per unit length is

$$C_{NT}^{\star} = \frac{C_{NT}}{L} = e^2 \cdot \text{DOS} \simeq 320 \,\text{pF/m} \quad \text{for } E \gg E_c.$$

(2.14)

The fraction  $C_{NT}/C_{ox}$  depends strongly on the thickness of the gate oxide. For a rather thick oxide layer, as the 400 nm we often used, the oxide capacitance is smaller than the quantum capacitance. For a simple approximation we estimate the fraction by using the values of Equations 2.12 and 2.14 to be on the order of  $\frac{C_{NT}}{C_{ox}} \approx 16$ . Note that the fraction depends on the Fermi energy and can deviate from the assumed constant value. This has to be considered in the subthreshold regime.

With this, we write the Fermi energy of the CNT in the silicon-oxide-NT structure as a function of the applied gate voltage:

$$E_f = e \frac{1}{1 + \frac{C_{NT}}{C_a}} (V_g - V_0)$$

(2.15)

where  $V_0$  is an offset voltage. Note that this does not exactly correspond to the threshold voltage as used in the experimental chapters. It is an artificial offset for the calculations below, that corresponds to the gate voltage needed to bring the Fermi Energy to the center of the band gap choosing a constant capacitances throughout band and band gap. Carbon nanotube FETs show a p-type behavior. For this reason hole conduction is considered here.

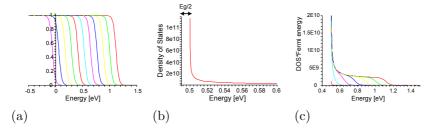

Next we calculate how many free carriers are induced into the CNT channel when a gate voltage  $V_g$  is applied. We consider the condition where the source-drain bias applied across the NT is small:  $eV_{sd} \ll k_BT \approx 25 \, \text{meV}$ . In this case we assume the potential along the CNT to be uniform. The product of the Fermi distribution and the density of available states (DOS) yields in the number of carriers per energy in the CNT. For the total number of free carriers in the CNT as a function of the Fermi energy we have to integrate over this product:

$$n(E_f) = \int DOS \cdot f(E_f) dE \qquad (2.16)$$

with the Fermi function (Figure 2.7 (a))

$$f = \frac{1}{1 + \exp\frac{E - E_f}{kT}}$$

and the density of states of a semiconducting CNT (see Appendix Equation A.14)

$$DOS(E) = \frac{8}{3\pi a_{CC} \gamma} \frac{|E|}{\sqrt{E^2 - (E_g/2)^2}} \Theta(|E| - E_g/2).$$

The DOS is plotted in Figure 2.7(b). Note that n is the number of charges per tube length as the 1D DOS is a density per length. The product DOS  $\cdot f(E_f)$  is plotted in Figure 2.7(c) for Fermi energy values belonging to different gating voltages as described in Equation 2.15.

**Figure 2.7:** (a) Fermi distribution f(E) for  $E_f$  given by Equation 2.15 at 300 K with  $\frac{C_{NT}}{C_g} = 16$ ,  $V_0 = 9$  V and  $V_g = -10, -8, ..., 10$  V.

- (b) Density of States for a NT with  $E_g = 1 \,\text{eV}$  (Equation A.14).

- (c) The product  $DOS \cdot f(E_f)$  for the same gate voltages as in (a).

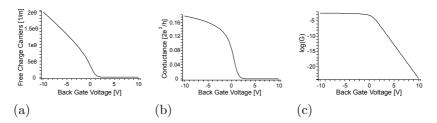

The integral 2.16 cannot be solved analytically. Results of numerical integration are shown in Figure 2.8 (a).

With the Drude model for diffusive transport we now can estimate the channel conductance:

$$G_{NT} = e \frac{n\mu}{L} \tag{2.17}$$

with the electron charge e, the length L of the CNT channel and the mobility  $\mu$ . Here we assume the mobility to be constant. The total resistance of a device is characterized by the sum of the CNT channel resistance  $R_{NT} = 1/G_{NT}$ , the quantum resistance  $\frac{h}{4e^2}$  and the contact resistance

Figure 2.8: (a) Number of free charge carriers (holes in this case), as function of applied gate voltage. (b) Conductance G and (c)  $\log(G)$  of CNT FET as function of applied gate voltage calculated by MOSFET model Equations 2.16 and 2.18. Parameters:  $V_0 = 9 \text{ V}$ ,  $\frac{C_{NT}}{C_g} = 16$ , temperature 300 K, contact resistance  $R_c = 50 \text{ k}\Omega$ , length of CNT channel  $L = 1 \mu\text{m}$  and mobility  $\mu = 2000 \text{ cm}^2/\text{Vs}$ .

$R_c$ . For this channel dominated model we assume the contact resistance to be constant. With this we obtain for the total conductance of the CNT FET

$$G = \frac{1}{\frac{h}{4e^2} + R_c + \frac{L}{e\mu n}}. (2.18)$$

The conductance G as a function of the applied gate voltage is plotted in Figure 2.8 (b) as calculated by Equation 2.18 using numerical integration for the number of carriers n.

Let's have a look at two regimes of Equation 2.18: the linear regime and the subthreshold regime where the Fermi energy is just below the band edge.

#### Linear G vs. $V_q$ regime

For high  $V_g$  the conductance is strongly suppressed. For high negative  $V_g$  the conductance saturates, limited by  $R_c$  and  $h/4e^2$ . In the linear regime of G vs.  $V_g$  in between, the total conductance is dominated by the channel

conductance given by Equation 2.17. From this we can calculate the slope as

$$\frac{dG}{dV_q} = \frac{e\mu}{L} \frac{dn}{dE_f} \frac{dE_f}{dV_q}.$$

The last term is given by Equation 2.13 and  $dn/dE_f$  can be derived from the integral 2.16. For energies well above the band edge we approach the Fermi function by a step function cutting off at  $E_f$  and then the derivative is  $dn/dE_f = DOS(E_f)$ . Inserting this together with Equation 2.13 we arrive at

$$\frac{dG}{dV_a} = \frac{e^2 \mu}{L} DOS \left( 1 + \frac{C_{NT}}{C_{ox}} \right)^{-1}.$$

With  $e^2 \cdot DOS = C_{NT}$  from Equation 2.14 we get

$$\frac{dG}{dV_q} = \frac{\mu}{L} \frac{C_{ox} \cdot C_{NT}}{C_{ox} + C_{NT}} \sim \mu \frac{C_{ox}}{L} \quad \text{for} \quad C_{ox} \ll C_{NT}.$$

(2.19)

In the linear region of G vs.  $V_g$  the slope of  $G(V_g)$  can be directly related to the carrier mobility  $\mu$  and the geometry of the device expressed in L and  $C_{ox}$ . In Section 4.2.3 this relation is used to determine the mobility of our CNT FETs.

#### Subthreshold regime

In the second case of the Fermi energy being below the band edge, only thermally exited charge carriers can contribute to a current. The number of carriers is determined by the Boltzmann factor  $e^{-(E_g/2-E_f)/(kT)}$ . Neither contact and quantum resistances nor the density of states are limiting. The conductance is given by  $G = e\mu/Ln_0e^{-(E_g/2-E_f)/(kT)}$ . If we take the derivative of the logarithm  $d(\ln(G))/dV_q$  we get

$$\frac{d(\ln(G))}{dV_g} = \frac{d(\ln(G))}{dE_f} \cdot \frac{dE_f}{dV_g} = \frac{1}{kT} \frac{dE_f}{dV_g}$$

In Section 2.1.4, the subthreshold swing S is defined as the gate voltage needed to suppress the current by one order of magnitude S

$dV_g/d(\log(I))$ . In the experimental part we generally plot the conductance at small bias voltage. So we have to transfer the above definition of S into conductance. Because the bias voltage is constant the conductance  $G = I/V_{sd}$  scales in the same way and we can say

$$S = \frac{dV_g}{d(\log(G))} = \ln 10 \frac{kT}{e} \frac{1}{\alpha}.$$

(2.20)

The efficiency parameter  $\alpha=e(dE_f/dV_g)$ . In the subthreshold region  $\alpha$  is constant. In the ideal case the Fermi energy follows the applied gate voltage and  $\alpha=1$ . Then the subthreshold swing is  $S\simeq 60\,\mathrm{mV/dec}$  at room temperature. In Figure 2.8(c) the logarithm of the conductance G is plotted against the back–gate voltage. In our simulation we find  $S\simeq 400\,\mathrm{mV/dec}$ . Note that a fixed  $\alpha=C_g/C_{NT}=1/16$  was assumed. In reality  $C_{NT}$  is expected to vanish in the subthreshold regime (see Section 2.2). For a device that is completely dominated by the channel resistance the subthreshold swing S could reach its ideal limit.

#### 2.3.3 CNT Schottky Barrier Transistor model

The modelling of carbon nanotube Schottky barrier transistors is more difficult than that for MOSFET devices and numerical simulation [20] is essential. Therefore a qualitative description will be presented.

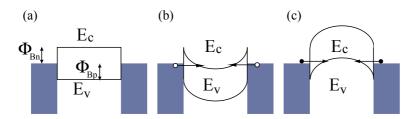

First we look at a mid-gap Schottky barrier structure. This means that the barriers to the conduction and valence bands are equal, as sketched in Figure 2.9 for the case of  $V_d=0$  and I=0. For  $V_g>0$  the conduction band is pushed down and electrons tunnel into the conduction band from both contacts. For  $V_g<0$  the valence band barrier is thinned and the hole tunnelling is increased. Note that the bands are bent towards the contacts and flat in the central region.

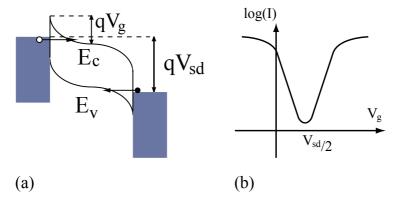

Consider now the case where a bias  $V_d$  is applied and  $V_g = V_{sd}/2$ . In this case the band diagram is symmetrical from left to right as sketched in Figure 2.10(a). At the left,  $V_g = V_{sd}/2$  and the left contact acts as a source of electrons. At the right contact,  $V_g = -V_{sd}/2$  and the right contact acts as source of holes. Holes and electrons flow in opposite directions, so

Figure 2.9: Schematics of CNT with metal contacts and Schottky barriers. Gate Voltage (a)  $V_g = 0$ , (b)  $V_g > 0$  and (c)  $V_g < 0$ ,  $\circ$  indicate electrons in the metal tunnelling into the CNT,  $\bullet$  indicate holes above Fermi energy of the metal.

Figure 2.10: (a) Schematics of CNT with metal contacts and Schottky barriers at  $V_g = V_{sd}/2$ . (b) Sketch of ambipolar current vs.  $V_g$  at fixed  $V_{sd}$ .  $\circ$ : electrons in the metal tunnelling into the CNT,  $\bullet$ : holes above Fermi energy of the metal.

the currents add. This is the minimum current of the Schottky barrier transistor. For  $V_g > V_{sd}/2$ , electron injection is enhanced and the device operates as an n-channel FET. For  $V_g < V_{sd}/2$  it operates as p-channel FET. The behavior sketched in Figure 2.10(b) of enhanced current for both, positive and negative gate potentials is called ambipolar behavior [21].

A symmetric ambipolar behavior can only be observed if the barriers between metal and CNT have the same height for holes and electrons. In CNT FET the most widely used contact metals Ti, Au and Pd have high barriers to the conduction band, but low barriers to the valence band. Therefore hole conduction is favored.

In this model the behavior of a CNT FET in the subthreshold region is by tunnelling through the Schottky barrier. As this barrier is modulated by the gate, the current through the nanotube in subthreshold region depends on the coupling of the gate to the barrier. This coupling is controlled by the gate capacitance  $C_{ox}^{\star}$ . The thicker the gate oxide is, the more the subthreshold swing S deviates from its ideal value of  $60\,\mathrm{mV/dec}$  (2.20) for a Schottky barrier dominated FET [22, 23]. For  $120\,\mathrm{nm}$  SiO<sub>2</sub> a subthreshold swing of  $S\sim2000\,\mathrm{mV/dec}$  was measured [17] (see Section 4.2.3 for more experimental details). This is a big disadvantage of Schottky barrier dominated CNT FETs compared to low contact CNT FETs.

#### 2.3.4 Experimental observations: Literature review

In literature both, channel dominated [24, 25] and Schottky barrier dominated devices [17] have been reported, and in many cases both effects might play a role [26, 27, 28]. Details of device geometry influence the effectiveness of the gate in modulating the carrier concentration in the channel [24] and in modulating the Schottky barriers [29, 17, 20]. Nanotube diameter and metal - nanotube contact critically determine the Schottky barrier height [30]. The role of the metal work function has been studied by different groups [25, 31, 30]. Pd makes very good contact for hole conduction [25, 32]. This is due to its good wetting properties

and its high work function (5.1 eV) which aligns the Fermi energy quite well with the CNT valence band. For Ti the Fermi energy lies deeper in the nanotube band gap, so that injection of both, holes and electrons is possible leading to ambipolar FETs. Quite good contact can be achieved by annealing [21]. Al has a low work function (4.1 eV) and the barrier to the conduction band is much smaller. Therefore electron transport is favored [31]. We designed our CNT FETs to have low contact barriers for holes as described in Section 3.2.

In summary the basic physics of MOSFET devices is described in Section 2.1 of this chapter. When scaling the devices down to nanowire like structures, the ratio  $C_s/C_{ox}$  has to be studied. In depletion  $C_s$  is given by the depletion capacitance  $C_d$  for bulk MOSFETs and deviates for nanowires of diameter  $d < W_d$ . For small nanowires  $d \ll L_D$  and for carbon nanotubes  $C_s$  is given by the quantum capacitance  $C_q$ . For CNT FETs a simple model is developed based on the standard MOSFET theory. It shows the basic physics. Assuming realistic values for  $\mu$  and  $R_c$  of high quality CNT FETs the quantitative outcome is in good agreement with observations described in Chapter 4.

# CHAPTER 3

## Sensor fabrication techniques

Silicon nanowire (SiNW) FETs and Carbon Nanotube (CNT) FETs were produced by different approaches: For SiNW FETs the structure was designed by lithography and transferred into the device layer of a Silicon on Insulator (SOI) wafer. CNT FETs were produced by localizing and contacting randomly grown carbon nanotubes (CNTs). Whereas the fabrication scheme for SiNW FETs is fully CMOS compatible, the approach used for CNTs can be used for research purpose only, as chemical vapor deposition of CNTs is not CMOS compatible and the fabrication scheme is sequential and very time consuming. Both processes are described below. Experimental details about the developement of processes can be found in Appendix C.

## 3.1 Silicon NW FET

Silicon Nanowire FETs (SiNW FET) were produced by etching the structure into the device layer of a SOI wafer. The silicon substrate — called handle layer — is used to apply a gate voltage and is therefore called back—gate.

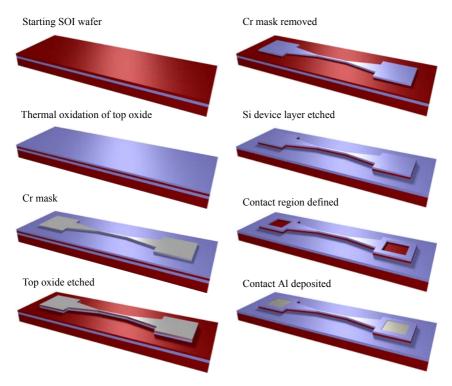

As starting material a SOI wafer with 150 nm buried oxide (BOX) and a 100 nm thick device layer was used. It was p-doped by boron with a resistivity of  $10-20\,\Omega{\rm cm}$  and was purchased from CSD Silicon. The fabrication of SiNW FETs is shematically shown in Figure 3.1. In short it contains the following steps:

- 1. Thermal oxidation of a 80 nm thick top silicon oxide layer. By this step the device layer is thinned to  $\sim 60$  nm.

- 2. Defining the etch mask of chromium:

- Structure of contact pads and connection leads defined by photolithography and deposition of 80 nm Cr.

- Structure of nanowires and small leads defined by e-beam lithography and deposition of 100 nm Cr.

## 3. Etching of the structure:

- Plasma etching of the top SiO<sub>2</sub> using the Cr layer as etch mask.

Plasma etching consists of a cleaning step of oxygen plasma, an unselective SiO<sub>2</sub> etching by a mixture of CHF<sub>3</sub> and oxygen plasma and a selective etching by CHF<sub>3</sub> that stops on the Si device layer.

- $\bullet$  The chromium mask is removed by wet etching with a mixture of NaOH, KMnO<sub>4</sub> and H<sub>2</sub>O (with a ratio 2:3:12) under constant shaking.

- The device layer is etched by Tetramethylammoniumhydroxide TMAH (25%) and 10% isopropanol in H<sub>2</sub>O at 45°C under constant stirring. A buffered HF dip just before this TMAH bath is needed to remove the native oxide.

Figure 3.1: Schematics showing the fabrication steps of Si NW FETs. The red color stands for Si, the blue one for  $SiO_2$ .

4. Contacts are created by a photolithography step to define the contact region, a buffered HF etching step to remove the top SiO<sub>2</sub> in the contact region, in situ Ar sputtering and deposition of 100 nm Al. The contacts have to be annealed at 450°C for 10 to 30 minutes to get ohmic contacts.

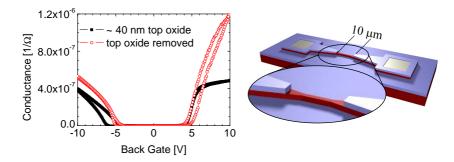

## 3.1.1 Top oxide

The top oxide is used as etching mask for the TMAH etching step and as protecting layer for the leads working in liquid environment. Thermal oxidation was performed at the PSI. The top oxide thickness is 70-80 nm. One can estimate the consumed Si to be  $0.46 \cdot x_{ox}$  [33]. This gives 33-37 nm of consumed Si and thus the remaining device layer is expected to be 62-68 nm thick. It is known that during the thermal oxidation of SOI wafers, some oxygen can diffuse through the device layer and lead to an increase of the buried oxide so that the device layer shrinks more than expected from conventional silicon wafer oxidation [34]. But this effect should be < 5 nm. The device layer thickness after oxidation is 60 nm, as measured by an Alpha-Step surface profiler.

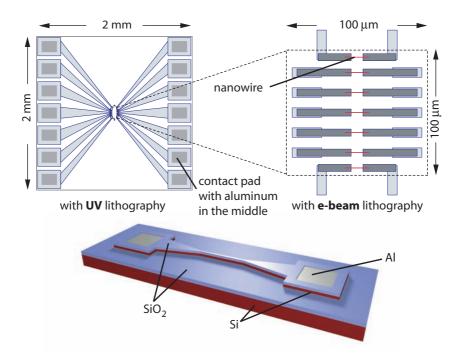

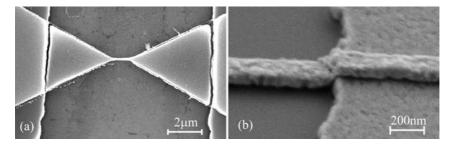

## 3.1.2 Etching mask

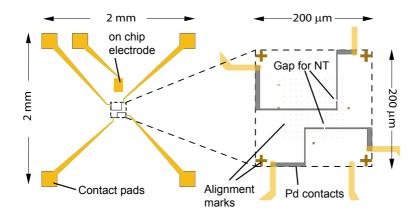

The structure of the mask can be seen in Figure 3.2. Contact pads are designed in a decent distance from the active region because for the use in sensing experiments, they have to be insulated from liquid. Contact pads, leads and alignment marks are designed by photo lithography. Nanowires are designed by e-beam lithography. The shape of the nanowire mask could be varied. Typical length is  $1-10 \,\mu\mathrm{m}$  and the width is  $\sim 80 \,\mathrm{nm}$ .

Chromium was chosen as etch mask because it can easily be evaporated and removed selectively to Si and  $\mathrm{SiO}_2$  by a simple wet etching step and it can easily be seen in the SEM. Organic masks like photo resist or e-beam resist lead to problems as they can hardly be removed after CHF $_3$  plasma etching. The thickness of the Cr film is chosen to be as thin as possible to minimize the aspect ratio of the mask of the nanowires. Limiting factor

Figure 3.2: Structure of mask for SiNW fabrication.

was the fact that the same Cr layer has to be used for alignment for the subsequent e-beam lithography step - and therefore the Cr mask has to be visible in the SEM even below the resist layer. The first evaporated Cr layer is chosen to be 80 nm. The second Cr layer is 100 nm and it is evaporated in three steps: 20 nm perpendicular and then twice 40 nm tilted by an angle of  $\pm 12^{\circ} - 15^{\circ}$  towards the two contacts to ensure good overlap with the first Cr layer (see Figure 3.3).

Figure 3.3: Overlay layer at metal evaporation. (a) Cr layer of 100 nm evaporated perpendicular on a Cr layer of 60 nm. It can be seen that the upper layer is not connected. (b) nicely connected 60 nm Au layer on top the same bottom Cr layer.

## 3.1.3 Etching of the device structure

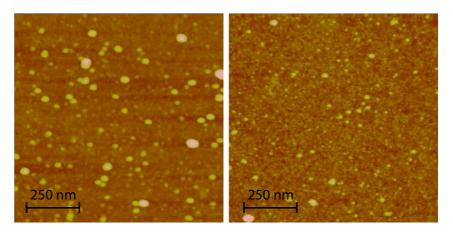

In a first step, the top  $SiO_2$  is etched using the Cr structure as etching mask. Before the the sample is cleaned by an oxygen plasma step of two minutes at a power of  $200\,\mathrm{W}$ . Then the  $SiO_2$  is etched by a CHF<sub>3</sub> plasma ( $40\,\mathrm{sccm}$  (standard cubic centimeters per minute) at  $25\,\mathrm{mTorr}$ ,  $100\,\mathrm{W}$  power) with addition of  $2\,\mathrm{sccm}$  of oxygen for  $90\,\mathrm{s}$  and for another  $2\,\mathrm{min}$  without oxygen. The oxygen is added since it was found that it makes the etched surface smoother. This can be seen by an AFM analysis shown in Figure 3.4. But when adding oxygen, the plasma etch does not stop at the Si layer any more, as one can see from the etching rates in Table 3.1. Therefore the last few nanometers of  $SiO_2$  are etched down to

Figure 3.4: AFM images of Si surface with top SiO<sub>2</sub> etched away. Left: the result of a CHF<sub>3</sub> plasma (40 sccm/min) process is shown. Right: the result of a mixed CHF<sub>3</sub> (40 sccm/min) and oxygen (2 sccm/min) plasma is shown.

the Si without addition of oxygen.

**Table 3.1:** Etch rates of CHF<sub>3</sub> plasma etch processes.

|                  | $SiO_2$             | Si                        | PMMA                       |

|------------------|---------------------|---------------------------|----------------------------|

| CHF <sub>3</sub> | $21\mathrm{nm/min}$ | $\sim 2.5\mathrm{nm/min}$ | $\sim 10  \mathrm{nm/min}$ |

| $CHF_3 + O_2$    | $21\mathrm{nm/min}$ | $\sim 8\mathrm{nm/min}$   | $\sim 30\mathrm{nm/min}$   |

When the top  $SiO_2$  is etched, the Cr mask can be removed by a wet etching step. A mixture of NaOH, KMnO<sub>4</sub> and H<sub>2</sub>O (with ratio 2:3:12) is chosen because it does not attack Si or  $SiO_2$  and because it etches both, chromium and chromium oxide [35]. It etches Cr with a rate of  $\sim 30 \, \text{nm/min}$ , after an initialization time of  $60-90 \, \text{s}$ . But to ensure that no Cr clusters are left, one has to etch several minutes in addition and strong stirring or shaking is needed. To avoid left overs sticking on the

surface, the first washing step after etching was done under shaking as well.

Before etching the device layer, the native oxide on the silicon has to be removed by a 20 s dip in buffered HF. A mixture of  $21 \,\mathrm{ml}$  HF (40%) +  $148 \,\mathrm{ml}$  H<sub>2</sub>O +  $155 \,\mathrm{g}$  NH<sub>4</sub>F was chosen for an etch rate of  $40 \,\mathrm{nm/min}$ .

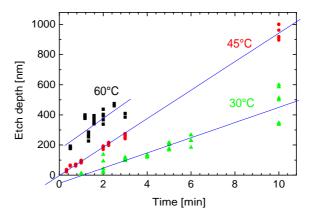

Tetramethylammonium hydroxide (TMAH) was chosen for etching the Si device layer because it is very selective to  $\mathrm{SiO_2}$  and etches anisotropically [36, 33]. It is very well suited for etching nanowire like structures [37]. With an etching rate of  $\sim 70\,\mathrm{nm/min}$  in Si  $\langle 100\rangle$  direction, a short etching time is enough to etch down the device layer. But an etching time of 15 min was used to ensure that TMAH etches to Si {111} surfaces. These are etched much slower and should build nice side walls of our nanowires (see Appendix C.1).

The etch rate depends very much on temperature so that it has to be controlled well. Therefore the etchant was stabilized in a temperature bath at 45° C. 10% 2-propanol was added to the TMAH solution (25% in  $\rm H_2O$ ) to reach smoother etching. Constant stirring is important to reach homogenous etching results. More details about TMAH etching are described in Appendix C.1.

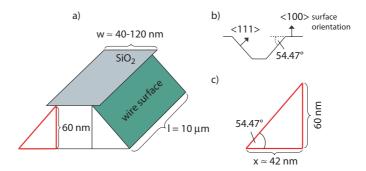

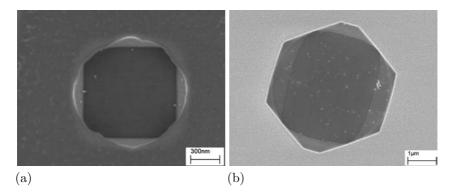

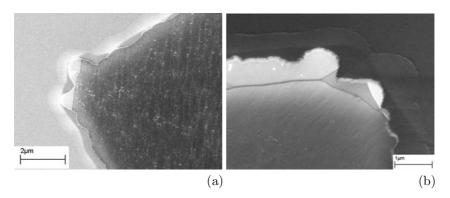

TMAH etches Si  $\{111\}$  planes much slower then other planes. On silicon (100) wafers the nanowires have to be oriented in a  $\langle 110 \rangle$  direction (see Appendix C.1) to ensure that the nanowire sidewalls are  $\{111\}$  planes. In this case the sidewall is not perpendicular to the top surface, but under an angle of  $54.47^{\circ}$ . This leads to a trapezoid like shape of the wire as shown in Figure 3.5. Typical dimensions are 60 nm for the height h and 40 nm to 120 nm for the width of the  $SiO_2$  mask. The top width of the nanowire is expected to be thinner due to underetching of the mask. Because of the trapezoid shape the bottom width is  $\sim 80$  nm wider than the upper part (see Figure 3.5(c)). The nanowire width was estimated by SEM and AFM as the examples of Figure 3.6 show. In case of thin masks or short TMAH etching one can clearly see that the bottom of the NW is wider than the mask. For longer etching times the undercut is too big so that the bottom width cannot be resolved. We estimate the mean width of the NWs to be in the range of  $W \sim 100$  nm typically.

Figure 3.5: Sketch of geometric dimensions. (a) Height  $h = 60 \,\mathrm{nm}$ , grey: SiO<sub>2</sub> mask, green: non vertical SiNW side wall. Geometrical proportion for anisotropic etching is shown in (b). The additional width at the bottom is geometrically well defined (c).

Figure 3.6: Images of two silicon nanowires. (a) From AFM one can estimate the bottom width of 136 nm for wire (a). (b) From SEM image the top width can be estimated to  $\sim 20 \, \mathrm{nm}$  for wire (b).

#### 3.1.4 Contacts

The contact region is defined by photo-lithography. The  $SiO_2$  is etched by buffered HF. This is better suited than plasma etching since it attacks the underlying Si less and when using CHF<sub>3</sub> plasma in combination with photo resist, the resist is hardened so that it cannot be dissolved after the etching step. To prevent HF to flow between the sample and the photo resist, an adhesion layer of hexamethyldisilazane (HDMS) is spun on the sample just before the photo resist. After photo lithography the HDMS is ashed in the open parts by  $3 \, \text{min}$  UV - ozone. This helps to remove leftover photo resist which is important for homogeneous etching.

The samples were built into the vacuum chamber of the evaporator just after removing the  $SiO_2$  to avoid oxidation of the Si. In addition the sample is sputtered with Ar plasma for 20 s short before evaporation of Al to remove any eventually new oxide in the contact region and to roughen the Si surface. 100 nm of Al is evaporated at low pressure ( $\sim 1 \cdot 10^{-7}$  mbar) with high rate to avoid oxygen to react with the Al.

After lift-off, the contacts are annealed at  $450^{\circ}$  C for 10-30 min in forming gas (mixture of Ar and  $H_2$ ) to form ohmic contacts.

## 3.1.5 Summary SiNW FET devices

Most SiNW FET sensors reported in literature are fabricated by a "bottom—up" approach of positioning and contacting grown SiNWs [38, 39] or in place growth [40]. In all these devices as well as in recently reported "top—down" fabricated structures [41, 42], the metal contact or heavily doped Si is in direct contact with the SiNW. This way the contact region is dominated by two effects: the geometrical confinement and the material junction. Here these two effects are separated by introducing semiconducting leads. A "top—down" approach to fabricate SiNW FETs has been developed with the following features designed for sensing experiments:

• Semiconducting leads ensure that there is no p-n or metal-semiconductor junction at the edge of the wire.

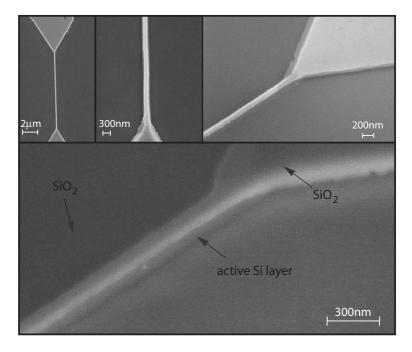

Figure 3.7: SEM picture of SiNW FETs with  $L=10\,\mu\mathrm{m}$  in top view (small images top left) and in side view.

- The SiNW channel is directly exposed to the environment so that it can be used for sensing.

- Top oxide avoids leakage currents between the leads when working in an electrolyte.

- The gate is insulated from the liquid by the buried oxide.

- Clean sidewalls are produced by TMAH so that a high aspect ratio (length:width > 100) can be reached for NWs in the range of  $W \sim 100$  nm.

- Standard SOI wafers with thin BOX and device layer can be used.

- The design is flexible and allows combination with on-chip electronics or microfluidics.

- The width of the SiNWs can be adjusted by controllable under etching of the SiO<sub>2</sub> mask in the TMAH wet etch process. This is important for application in the field of sensing. As we will show in Section 5.1.2, the sensitivity of the SiNW response to a change in surface potential can be tuned by adjusting the wire width. Controlling the width by etching would allow combining SiNW FETs of varying sensitivity to enhance the dynamic range.

Figure 3.7 shows SiNW FETs with  $L = 10 \,\mu\text{m}$ . The top SiO<sub>2</sub> can bee seen in all pictures, the Si sidewall can be recognized in the two pictures of viewing under a tilt angle.

## 3.2 Carbon Nanotube FET

The fabrication of SWNT Field Effect Transistors is illustrated in Figure 3.8. SWNTs were grown by Chemical Vapor Deposition (CVD) on Si wafers with 400 nm thermally grown  $\mathrm{SiO}_2$ . Then alignment markers and bonding pads of  $\mathrm{SiO}_2/\mathrm{Ti}/$  Au were prepared. SWNTs were selected and located by SEM. Then the SWNTs were contacted by Pd or Ti / Au. For

the passivation of the contacts different schemes were used as described in Section 5.6.1. The first subsection gives a general overview of fabrication issues of carbon nanotube FETs (CNT FETs) to justify the chosen approach. More details about our fabrication scheme can be found in the following Subsections (3.2.2-3.2.4), alternative fabrication approaches are described in Appendix C.3.

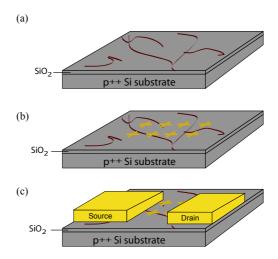

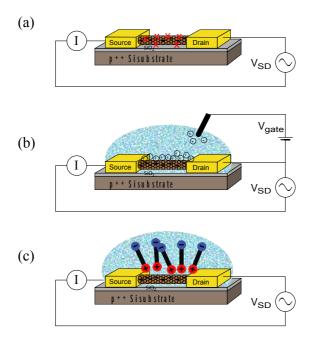

Figure 3.8: Fabrication Scheme for CNT FETs: (a) CNT growth, (b) patterning of markers, (c) deposition of metal contacts

## 3.2.1 General device fabrication issues

Today's processes for device fabrication of CNT FETs of individual SW-NTs are far away of being efficient and reliable. Many different approaches for efficient and controllable device fabrication are under investigation. One issue is how to place and align CNTs where they are needed, another issue is how to get a specific type of CNTs. A third issue is the compatibility of CNT device fabrication with CMOS technology. All these issues

have to be addressed for the two possible main routes of growing CNTs directly on the substrate and of deposing CNTs from solution.

#### Positioning of CNTs

In CVD growth of CNTs their position can be chosen by selective positioning of catalyst. Many different approaches have been examined. Among them are: Conventional lithography and lift-off technique for rather big catalyst islands [32], micro contact printing [43] and self assembly of iron containing macromolecules [44].

Orientation of CNTs during CVD growth was achieved by gas flow [45], by an electric field or by growth along crystaline steps of the substrate [46]. I regularly observed orientation of nanotubes with laminar gas flow, but only for very long tubes ( $\geq 100 \, \mu \text{m}$ ).

Selective positioning of nanotubes from solution was achieved by dielectrofloresis [47], by tuning the hydrophobicity of metal and substrate with self assembled molecular monolayers [48, 49, 50] or by molecular recognition of modified CNTs with modified contacts [51, 52].

As all these techniques are not yet fully developed, we design the contacts to fit to randomly grown tubes. This is a time consuming process but allows to control that only a single tube bridges the contacts.

## Selection of CNT Type

In CVD of SWMNTs the diameter can be controlled by the size of the catalyst particles and by the chosen temperature [53, 54, 55]. In this way the diameter distribution can be tuned well. But to narrow down the distribution is a task which is still under hard investigation [53]. To narrow down the distribution to the level of chirality selectivity, other parameters have to come into play that help stabilizing the growth like co-catalysts or stabilizing effects of the substrate [56].

Solving SWNTs in water with single-stranded DNA oligomers as surfactant is diameter dependant. Using different DNA sequences SWNTs of

different diameter could be separated [57]. Metallic or semiconducting CNTs could be deposited with high selectivity by dielectrophoresis [47]. A very critical issue in deposing SWNTs from liquid is to avoid bundeling. A lot of studies can be found about solvents, surfactants and deposition methods [58, 59, 60].

Some effort in fabrication of CNT FETs with tubes from solution is discussed in Appendix C.3. Finally we decided to grow tubes by CVD as described in Section 3.2.2.

#### CMOS technique compatibility

For CVD growth of SWNTs directly on chip the high temperatures required for the decomposition of the gases is destructive for any CMOS based chip. Efforts are put in bringing down the required temperature of CVD by choice of catalyst and by plasma enhanced CVD. Such principle based incompatibilities can be avoided in liquid based deposition of nanotubes. But in the process of separation and selective positioning of CNTs from liquid, chemicals are needed that are far from being desired in any CMOS compatible clean room. For our research purpose none of these restrictions are relevant.

CVD growth on substrate and deposition of CNTs were both tested (see Appendix C.3) but finally we stick to CVD growth as described in the next Section.

## 3.2.2 Chemical Vapor Deposition

Different techniques can be used to produce Carbon Nanotubes: Arcdischarge, laser ablation, High Pressure Carbon dioxide growth and catalytic Chemical Vapor Deposition (CVD) of hydrocarbons. The last method was chosen because CNTs can be grown on the substrate directly. All other production methods give a CNT powder that has to be purified, suspended in solvents and then deposited on a suitable substrate. There remain many problems in a solution-based device fabrication process. First, the nanotubes have to be purified. This normally involves strong acid treatment and sonication, which may introduce defects into the nanotubes and cut them into short pieces. Secondly, nanotubes tend to bundle and surfactants are used to separate them efficiently, but surfactants are not desired for contacting the nanotubes.

By CVD, carbon nanotubes can be grown horizontally on the substrate and are clean enough so that they can be contacted without any purification step, which greatly reduces the possibility of defect formation of SWNTs. Measurements in our group and others have shown that devices made of CVD nanotubes grown directly on substrates tend to exhibit better performance than those produced using SWNTs prepared by other methods [61]. One of the reasons is the large diameter that CVD tubes typically have [30], another reason is that surfactants used in the deposition can lead to an additional contact resistance.

The CVD process is based on the method developed in the group of H. Dai [62]. The substrate covered with a catalyst of FeNO<sub>3</sub>,  $MoCl_2O_2$  and  $AlO_2$  (preparation recipe in Appendix C.2) is heated in a furnace to  $900^{\circ}$  C –  $1000^{\circ}$  C under Ar flow. Hydrogen and the feeding gas (methane) are flown during 10 min for CNT growth.

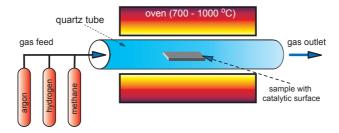

Figure 3.9: Scheme of CVD setup used for growth of carbon nanotubes.

The CVD furnace is sketched in Figure 3.9. Catalyst is spun on a freshly cleaned wafer. The samples are introduced into the quartz tube on a small boat. The gases are fed into the system by a pressure of 0.1 bar above

atmospheric pressure. A water bubbler at the outlet gives us control over the flow and avoids environmental gases to diffuse into the system.

Argon runs during heating up and cooling down ( $800 \, \mathrm{sccm/min}$ ). Different growth temperatures were used, but best results were achieved with a temperature of  $950^{\circ}\,\mathrm{C}$ . During growth, argon was switched off. Methane ( $1300 \, \mathrm{sccm/min}$ ) and hydrogen were flown for  $10 \, \mathrm{min}$ . After growth methane is replaced by argon, but hydrogen still runs while cooling down to  $550^{\circ}\,\mathrm{C}$ . From this temperature down to about  $200^{\circ}\,\mathrm{C}$  only argon flows.

The temperature during growth has to be high enough to ensure that there are only SWNTs, not double-walled or multi-walled. But if temperature is too high, amorphous carbon is deposited. Hydrogen reduces the deposition of amorphous carbon, but it competes with the growth process [63]. Therefore the flow of hydrogen was chosen moderately. For more details see Appendix C.2.

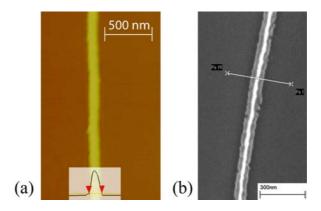

#### 3.2.3 Selection and location

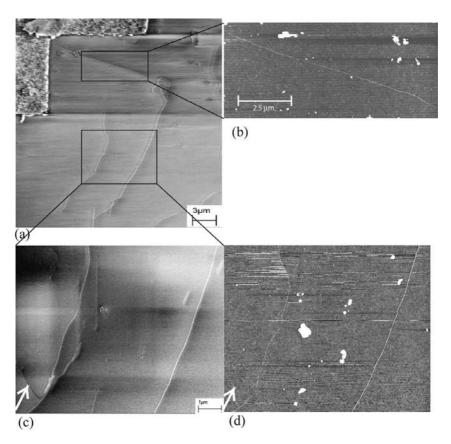

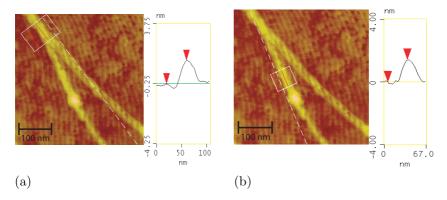

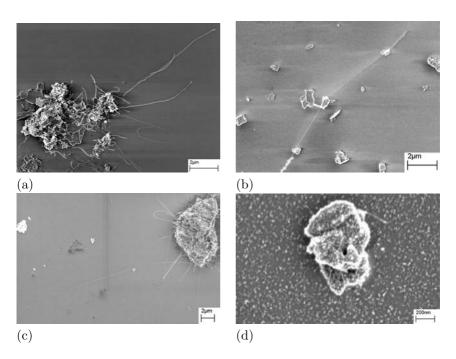

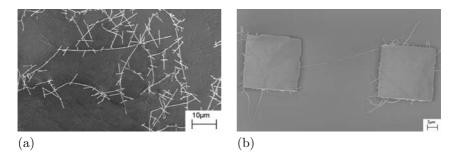

Scanning Electron Microscopy (SEM) was used to select and locate SW-CNTs. A typical acceleration Voltage of 1 kV was used to image SWNTs on silicon wafers with SiO2. At such low acceleration voltage the used SEM (LEO Supra 35) has a resolution limit of about ten of nanometers. Still individual carbon nanotubes can be seen. To check that we see all the SWNT in SEM, a comparison between a SEM and AFM image of the same sample is shown in Figure 3.10.

The advantage of the AFM is its much higher resolution that the SEM. To prevent damaging the tubes tapping mode AFM was chosen. The SEM is however much quicker and easier to be used than the AFM. One can be relatively sure that every tube can be seen in an AFM scan of the surface but it was not obvious if they would appear on SEM pictures due to lower resolution of the SEM. By scanning the same area using AFM and SEM and comparing the results it was estimated if everything could be also seen in the SEM images.

Figure 3.10: SEM (a) and (c) and AFM (b) and (d) pictures of the same region. In SEM the CNTs can be seen even at quite low magnification due to their high contrast to the background. The AFM has a much higher resolution and the background is imaged much more detailed. It even makes it hard to see the tubes. The very small tube indicated with an arrow in (c) and (d) is harder to find in the AFM picture (d) then in the SEM picture (c). (CNTs grown by methane at 950° C.)

Practically all tubes that are seen in AFM can also be seen in SEM. This is an important result. In SEM the CNTs can be seen even at quite low magnification due to their high contrast to the background. The high contrast comes from the different electronic properties of CNTs and the silicon oxide substrate. It depends very much on the acceleration voltage. At low voltage tubes seem bright when looking at backscattered electrons. The AFM has a much higher resolution and the background is imaged in much more detail. The surfactant or catalyst particles lying around are much bigger than the CNTs and therefore the feedback system of the AFM cannot be optimised to image the CNTs. This makes it even harder to see the small tubes. But we are pretty convinced that by careful imaging both, AFM and SEM can show all the tubes. According to this the SEM can be used to scan samples for nanotubes. One can localise the nanotubes for contacting and roughly estimate from the SEM pictures if the nanotubes are likely to be individual or not.

An open question is still how invasive the e-beam exposure is on CNTs. Strong influence of e-beam exposure of carbon nanotubes has been reported [64, 65], mainly for high voltages. But the good properties of the nanotube FETs produced this way show that short imaging does not strongly affect them. Even exposing contacted nanotubes to an e-beam dose of  $500\,\mu\mathrm{As/cm^2}$  at  $35\,\mathrm{kV}$  does not influence their conducting properties (See Section 5.6.1).

## 3.2.4 Contacting CNTs

Two steps of lithography and metal deposition were used. A typical structure of the first one is shown in Figure 3.11 in yellow. It shows the bonding pads, long leads to the inner part and small alignment markers and a side gate designed for electrolyte gating. On this structure  $10\,\mathrm{nm}$  SiO<sub>2</sub>, a  $10\,\mathrm{nm}$  Ti adhesion layer and about  $40\,\mathrm{nm}$  Au were deposited. Sometimes bundles of nanotubes with a length of several hundred micrometers made a short between the leads. The SiO<sub>2</sub> below the leads insulated the leads from these tubes and prevented from shortage problems.

In a second lithography step the contact leads were designed to contact

Figure 3.11: Mask for metal deposition for CNT FETs.

the selected nanotubes to the leads defined in the first step. The structure is shown in Figure 3.11 in grey. These contacts are made by Ti / Au or Pd. The latter is chosen mostly as it makes much better contacts due to its wetting properties and because the work function matches nicely the CNT band gap.

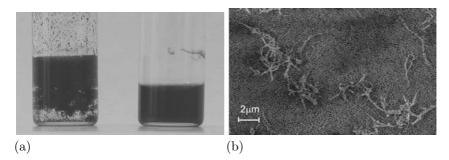

## 3.2.5 Summary CNT FET fabrication

As an optimal fabrication approach for CNT FETs for sensing purpose CVD was chosen for the following reasons:

- CVD tubes can be used as grown, no purification and no surfactant is needed that would alter the surface properties.

- Tubes grown on substrate bundle less than CNTs in powder and solution.

- CVD results in CNTs of rather high diameter of  $\sim 1-3\,\mathrm{nm}$ . This

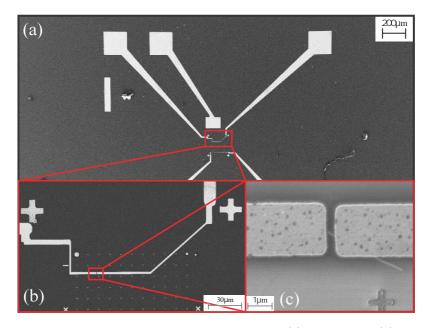

Figure 3.12: SEM images of a CNT FET. Overview (a) with zoom in (b) showing alignment marks and contacting leads. (c) is a zoom in of (b) showing the gap with the CNT bridging.

favors high contact transparency. Good conducting properties of CNTs from our CVD process are shown in the next chapter.

CNTs are localized by SEM before contacting so that we are sure that only one tube bridges the contacts. Palladium was chosen as contact metal for its good contact properties. SEM pictures of a CNT FET are shown in Figure 3.12.

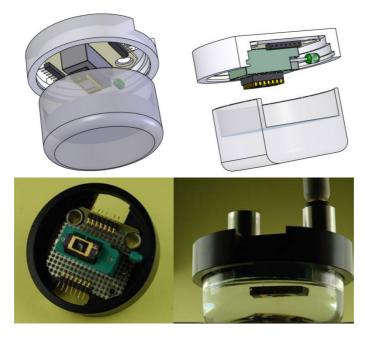

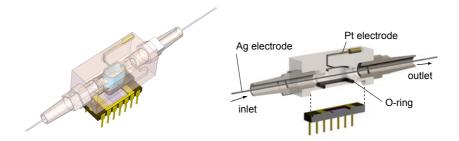

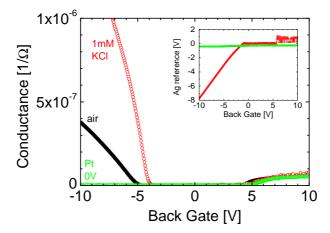

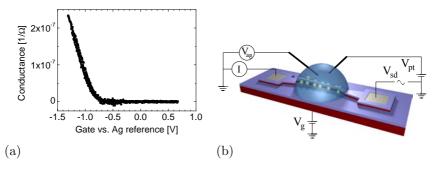

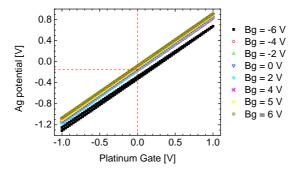

## 3.3 Packaging

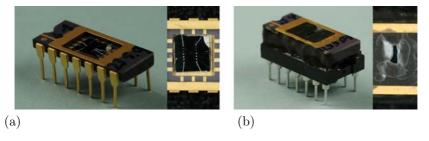

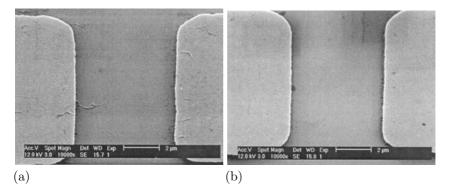

All devices were glued on a chip carrier and wire bonded with Al wire as can be seen in Figure 3.13(a). To contact the silicon backside it was scratched with a diamond scriber to get a fresh, unoxidized silicon surface. Then silver paint or silver epoxy was used to glue it on the chip carrier or to create a big conducting pad. The pad or chip carrier ground plate can be contacted by wire bonding.

Devices that were used in liquid were sealed with epoxy. Epoxy was placed manually to cover the bonding wire and pads as shown in Figure 3.13(b). In this way only the lithographically defined leads and the nanowires or nanotubes were exposed to the liquid. As epoxy, Bectron PK 4342 was used for working in aqueous environment or standard solvents and TorrSeal was used to work in benzene and chloroform.

Figure 3.13: A chip on the chip carrier (a) before and (b) after packaging.

# CHAPTER 4

## Characterization of SiNW and CNT FETs

Device properties of the SiNW and CNT FETs described in Chapter 3 are discussed here. The silicon substrate is used as back–gate to modulate the conduction of the SiNW or CNT channel. Main focus is put on the small bias regime as this will be used in sensing experiments described in Chapter 5. The two FET types are characterized separately in two sections. A comparison will be given in Chapter 6.

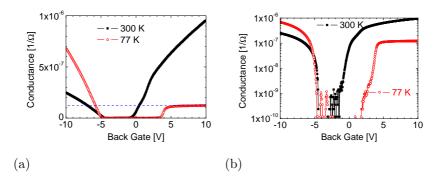

## 4.1 Silicon Nanowire FET characterization

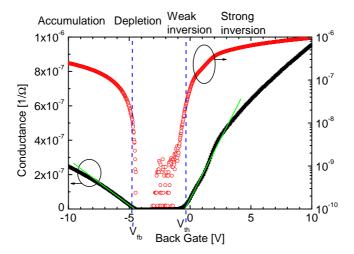

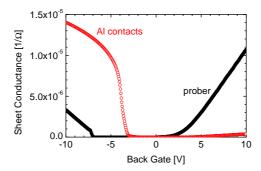

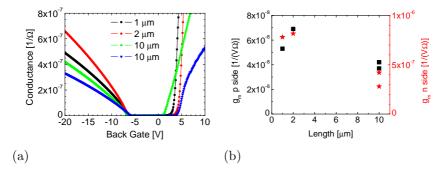

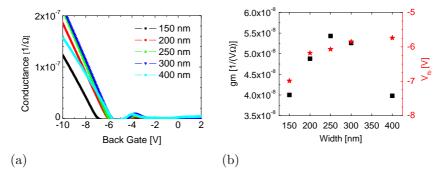

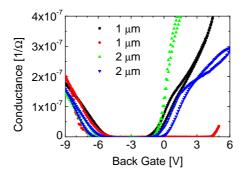

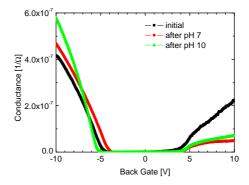

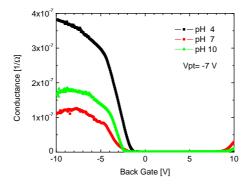

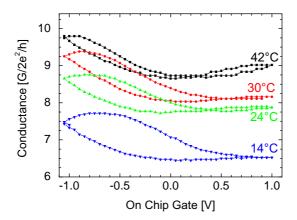

The main features of Silicon Nanowire (SiNW) FETs can be found in the transfer characteristic, which is the conductance G of the nanowire as function of applied gate voltage  $V_g$  as shown in Figure 4.1. Measurements

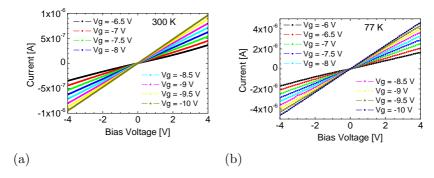

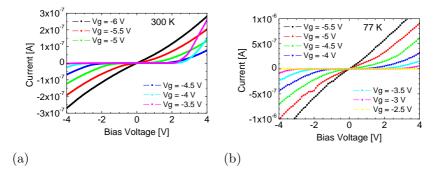

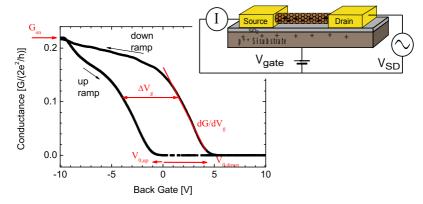

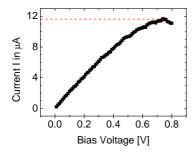

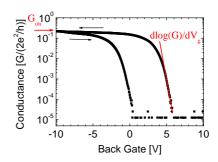

of the transfer characteristics were always performed at zero dc bias voltage on source–drain, but with a small ac voltage  $V_{ac}=10\,\mathrm{mV}$ . In the back–gate configuration the gate voltage is applied via the handle–wafer. At negative back–gate voltages holes are induced in the channel. As the device is p-doped this is the accumulation region. The onset voltage for the accumulation region corresponds to the flat band voltage  $V_{fb}$ . It can be found by extrapolating a linear fit of G vs.  $V_g$  to zero conductance. The slope of such a linear fit is called transconductance  $g_m$ . In the depletion region the current drops exponentially with the gate voltage. A sketch of the charge distribution in these regimes is shown in Figure 4.2. As the nanowire is very thin there is a big region where the conductance is suppressed completely [66]. A further increase of  $V_g$  leads to weak and strong inversion with an exponential part and a linear part in the transfer characteristic. The onset voltage of strong inversion is called threshold voltage  $V_{th}$ . It can be extracted by a linear fit of G vs.  $V_g$  at zero conductance.

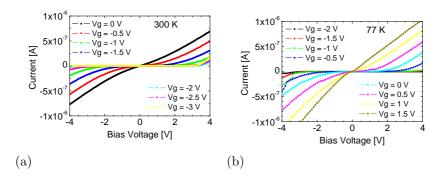

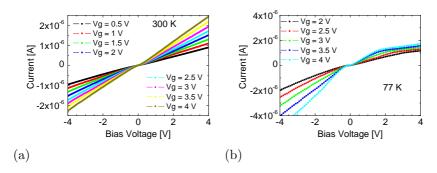

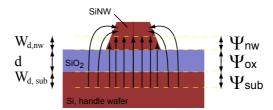

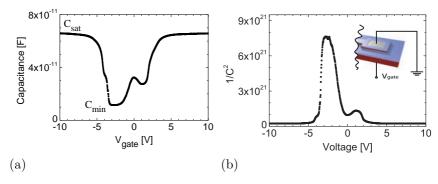

Each of these regimes is now described in more details analyzing measurements of conductance vs. back–gate at room temperature and 77 K and current vs. bias measurements. Then the gate capacitance, effects of varying geometry and hysteresis in back–gate response are described.

## 4.1.1 Accumulation regime

In accumulation the current is proportional to the applied gate voltage (see Equation 2.1)

$$I = \frac{W}{L} \mu C'_{ox} (V_g - V_0) V_{sd}$$

(4.1)

with the nanowire width W, length L, the hole mobility  $\mu$ , the gate oxide capacitance per unit area  $C'_{ox} = C_{ox}/A$ , the applied gate voltage  $V_g$ , an onset gate voltage  $V_0$  and the applied source - drain bias voltage  $V_{sd}$ . This relation holds for small bias voltages.

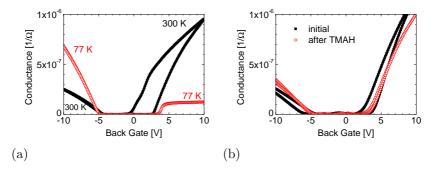

An effective device mobility  $\mu_{dev}$  at zero bias can be extracted from the transfer characteristic shown in Figure 4.3(a) for room temperature and liquid nitrogen temperature (77 K). In the accumulation regime the slope of a linear fit is given by the derivative of Equation 4.1. Using  $G = I/V_{sd}$

Figure 4.1: Conductance vs. back—gate voltage for a typical SiNW FET of  $L=10\,\mu\mathrm{m}$ .  $\blacksquare$ : linear dependance indicated by the left scale,  $\stackrel{\textstyle \text{O}}{}$ : logarithmic dependance indicated by the right scale.  $V_{sd}$ : 0 V dc,  $10\,\mathrm{mV}$  ac (317 Hz).

we get  $dG/dV_g = d(I/V_{sd})/dV_g = W/L \cdot \mu_{dev} C'_{ox}$ . From this, the hole mobility is

$$\mu_{dev,h} = \frac{L}{W} \frac{1}{C'_{ox}} \frac{dG}{dV_g}.$$

(4.2)

With a length  $L=10\,\mu\mathrm{m}$  of this specific SiNW, a width of 100 nm and the gate capacitance  $4.7\cdot10^{-4}\,\mathrm{F/m^2}$  as typical value (see Section 4.1.5 for more details), we get

$$\begin{array}{lll} \mu_{dev,h}(300\,{\rm K}) & \sim & 100\,{\rm cm^2/Vs}, \\ \mu_{dev,h}(77\,{\rm K}) & \sim & 320\,{\rm cm^2/Vs}. \end{array}$$

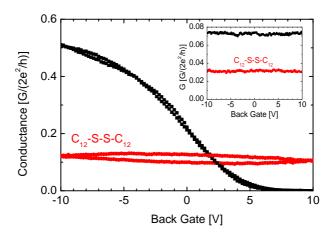

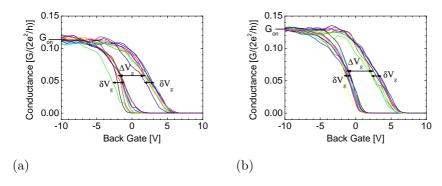

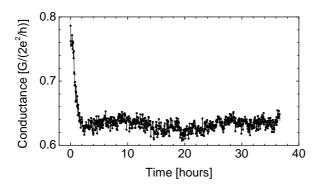

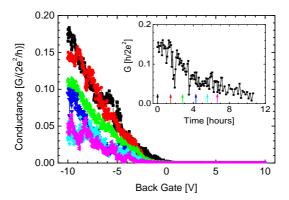

The effective device mobility is higher at  $77\,\mathrm{K}$  because of reduced electron—